接口

线性空间

部署

云原生

devops

费用流

激活函数

web大学生网页作业成品

momentum

mysql存储过程

自动批量下载图片的插件

类模板

CAPL

localStorage使用

拆包

自定义Starter案例实操

Firebase

Verilator

Sentieon

效率提升

数字电子技术

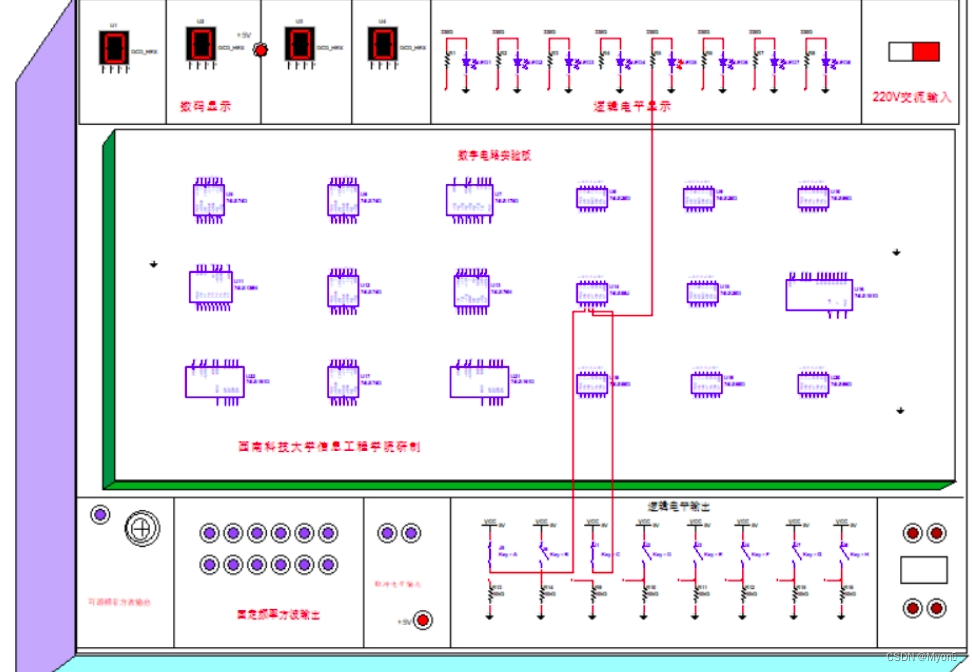

2024/4/29 4:36:55西南科技大学数字电子技术实验三(MSI逻辑器件设计组合逻辑电路及FPGA的实现)FPGA部分

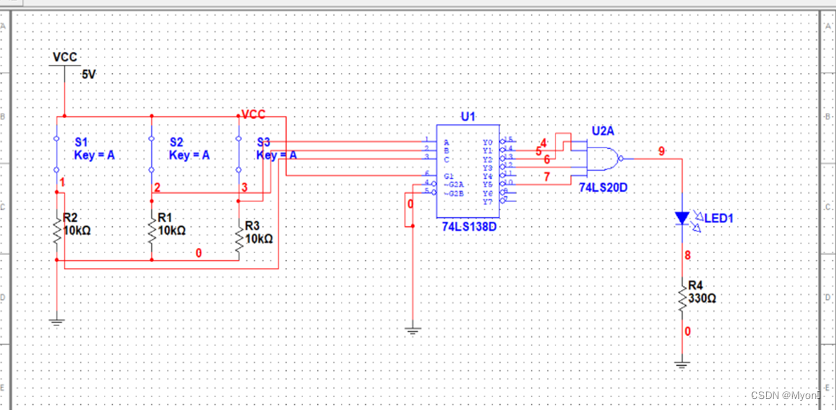

一、实验目的 进一步掌握MIS(中规模集成电路)设计方法。通过用MIS译码器、数据选择器实现电路功能,熟悉它们的应用。进一步学习如何记录实验中遇到的问题及解决方法。二、实验原理

1、4位奇偶校验器 Y=S7i=0DiMi

D0=D3=D5=D6=D

D1=D2=D4=D7= `D 2、组合逻辑电路 F=A`B C …

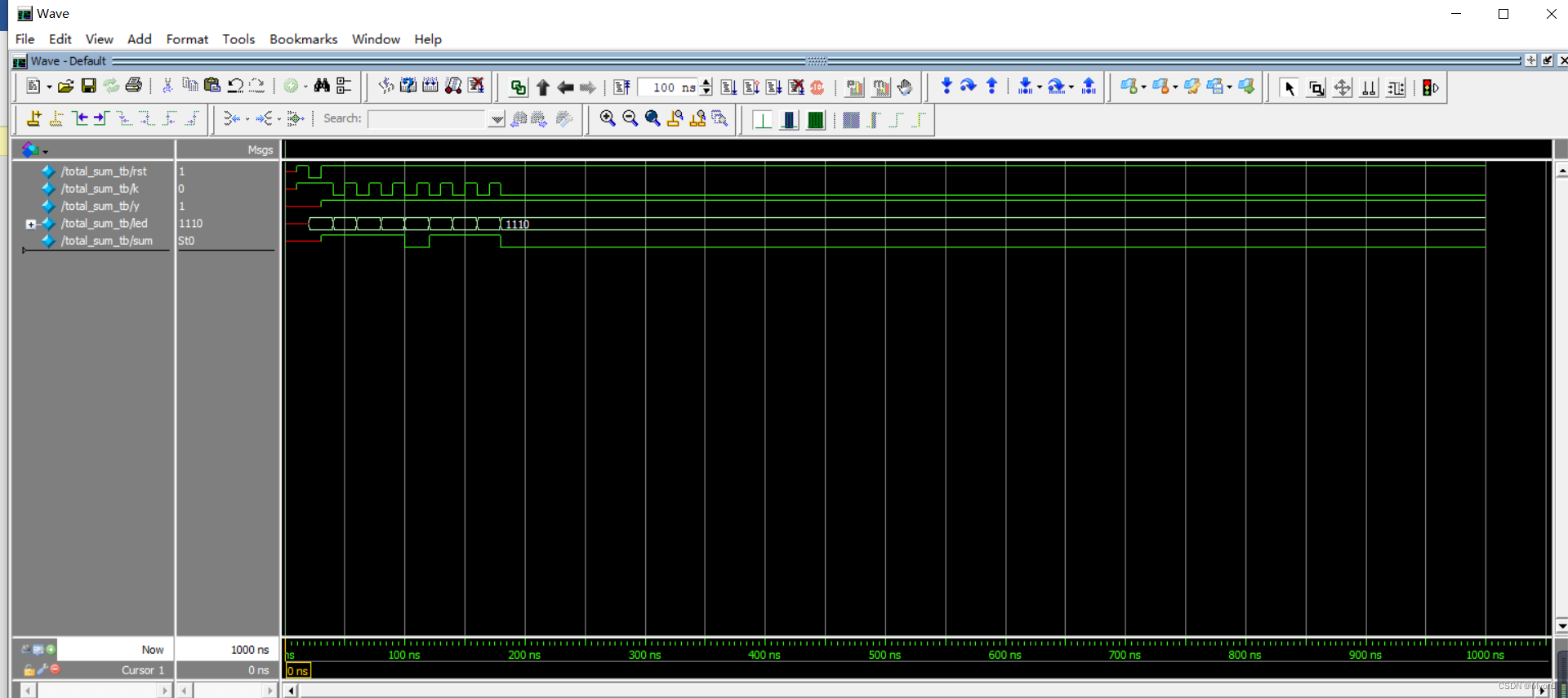

西南科技大学数字电子技术实验七(4行串行累加器设计及FPGA实现)FPGA部分

一、实验目的

1、掌握基于Verilog语言的diamond工具设计全流程。

2、熟悉、应用Verilog HDL描述数字电路。

3、掌握Verilog HDL的组合和时序逻辑电路的设计方法。

4、掌握“小脚丫”开发板的使用方法。

二、实验原理 三、程序清单(每条语句必须包括注释或在开发…

8位LED流水灯设计

一、实验目的 本实验为设计性实验,要求理解和掌握触发器、译码器、时序脉冲、LED显示单元的工作原理与功能,通过设计和制作8位的LED流水灯电路,综合运用触发器和译码器等逻辑器件及显示单元进行功能性时序逻辑电路的设计和制作,掌握时序逻辑电路的基本设计和调试方法。 二、…

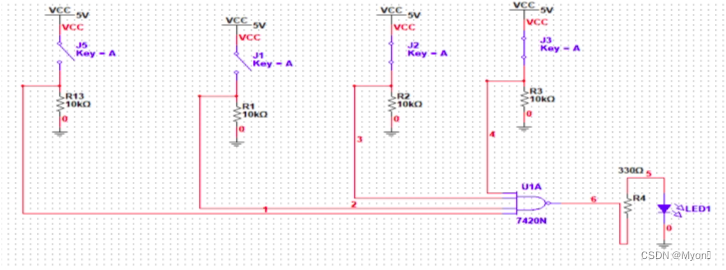

实验一 门电路逻辑功能及测试

一、实验目的 1.熟悉门电路逻辑功能. 2.熟悉数字电路学习机及示波器使用方法。

二、实验仪器及材料 1.双踪示波器 2.器件 74LS00 二输入端四与非门 2片 74LS20 四输人端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片

…

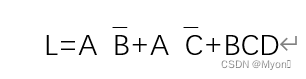

西南科技大学数字电子技术实验三(MSI逻辑器件设计组合逻辑电路及FPGA的实现)预习报告

一、计算/设计过程

说明:本实验是验证性实验,计算预测验证结果。是设计性实验一定要从系统指标计算出元件参数过程,越详细越好。用公式输入法完成相关公式内容,不得贴手写图片。(注意:从抽象公式直接得出结果,不得分,页数可根据内容调整)

1、4位奇偶校验器

真值表 …

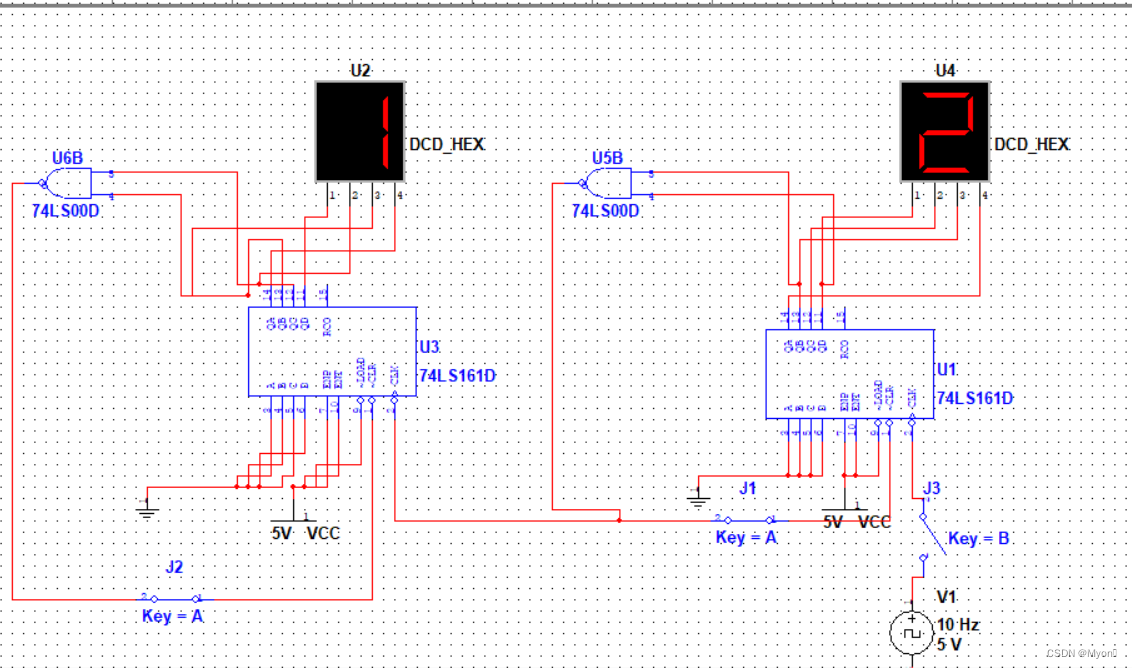

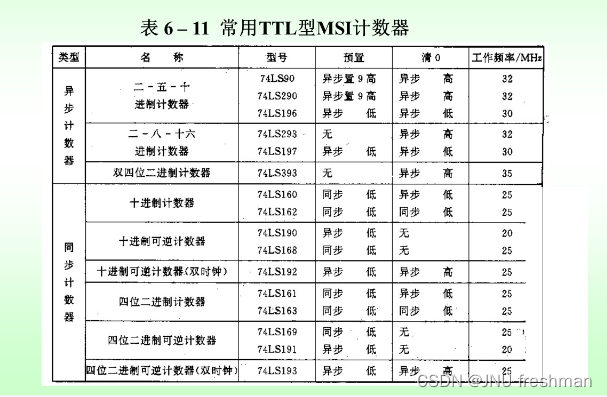

西南科技大学数字电子技术实验五(用计数器设计简单秒表)FPGA部分

一、实验目的

1.进一步理解用中规模集成计数器构成任意进制计数器的原理。

2.了解计数器的简单应用。

3.进一步学习与非门和译码显示器的使用方法。

4.学会用FPGA实现本实验内容。

二、实验原理 简单秒表 可暂停、复位秒表

三、程序清单(每条语句必须包括注释或在开发…

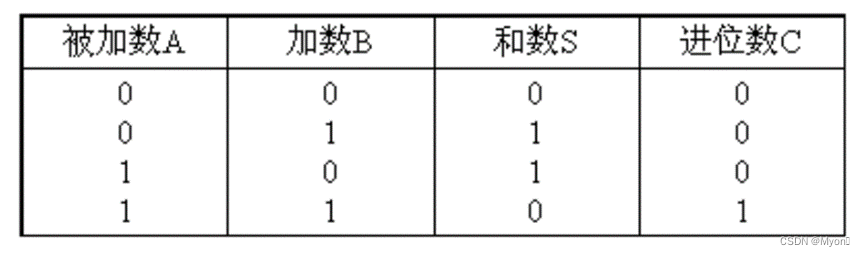

西南科技大学数字电子技术实验二(SSI逻辑器件设计组合逻辑电路及FPGA实现 )预习报告

一、计算/设计过程

说明:本实验是验证性实验,计算预测验证结果。是设计性实验一定要从系统指标计算出元件参数过程,越详细越好。用公式输入法完成相关公式内容,不得贴手写图片。(注意:从抽象公式直接得出结果,不得分,页数可根据内容调整)

1、1位半加器

真值表: 逻…

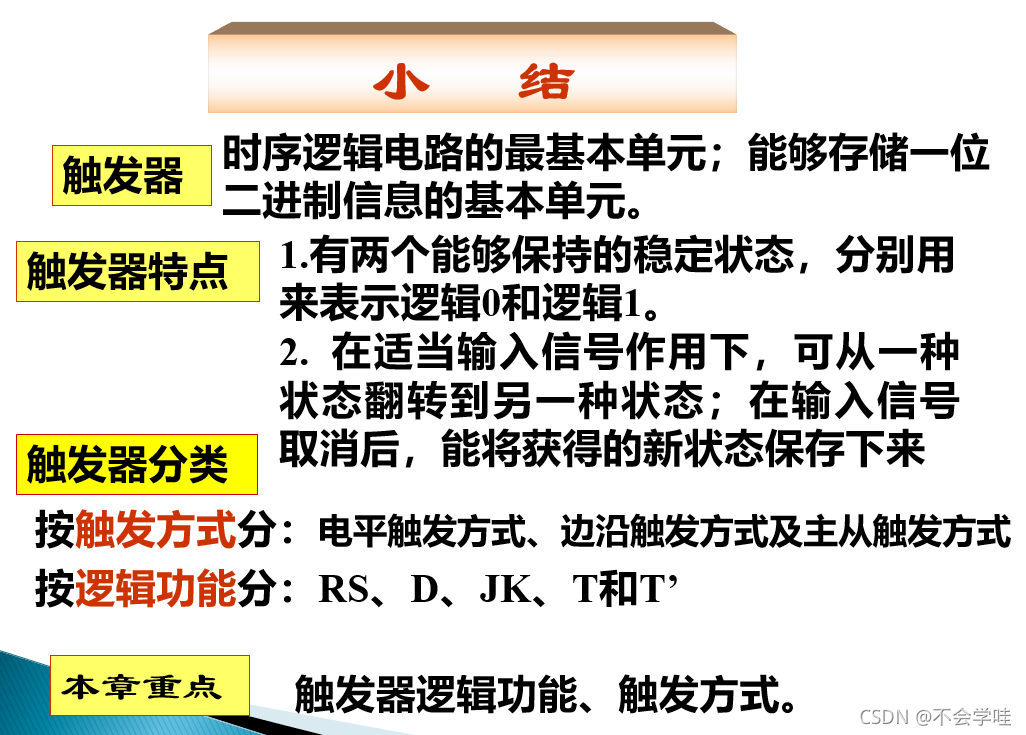

数字电子技术期末知识点总结

文章目录 时序逻辑电路时序电路的分析同步时序电路的分析例子1(有输入输出)例子2 (只有输出)例子3(没有输入、输出) 异步时序电路的分析例子1 小结 时序电路的设计同步时序电路的设计串行数据检测器JK 触发…

西南科技大学数字电子技术实验二(SSI逻辑器件设计组合逻辑电路及FPGA实现 )FPGA部分

一、实验目的

1、掌握用SSI(小规模集成电路)逻辑器件设计组合电路的方法。

2、掌握组合逻辑电路的调试方法。

3、学会分析和解决实验中遇到的问题。

4、学会用FPGA实现本实验内容。

二、实验原理

包括:原理图绘制和实验原理简述

1、1位半加器 2、1位全加器 3、三…

西南科技大学数字电子技术实验一(数字信号基本参数与逻辑门电路功能测试及FPGA 实现 )预习报告

手写报告稍微认真点写,80随便有

目录 一、计算/设计过程

1、通过虚拟示波器观察和测量信号

2、通过实际电路(电阻、开关、发光二极管)模拟逻辑门电路

二、画出并填写实验指导书上的预表

三、画出并填写实验指导书上的虚表

四、粘贴原理…

西南科技大学数字电子技术实验一(数字信号基本参数与逻辑门电路功能测试及FPGA 实现)FPGA部分

一、 实验目的

1、掌握基于 Verilog 语言的 diamond 工具设计全流程。

2、熟悉、应用 Verilog HDL 描述数字电路。

3、掌握 Verilog HDL 的组合和时序逻辑电路的设计方法。

4、掌握“小脚丫”开发板的使用方法。

二、 实验原理

与门逻辑表达式:Y=AB

原理仿真图: 2 输入…